DDR5 voor pc’s, laptops en servers: wat biedt het?

De huidige computers gebruiken DDR4-SDRAM als werkgeheugen, maar DDR5 zal naar verwachting dit jaar beschikbaar komen met een snellere data-overdracht, hogere capaciteit, dualchannel-modus en een hele reeks kleine verbeteringen.

Lees verder na de advertentie

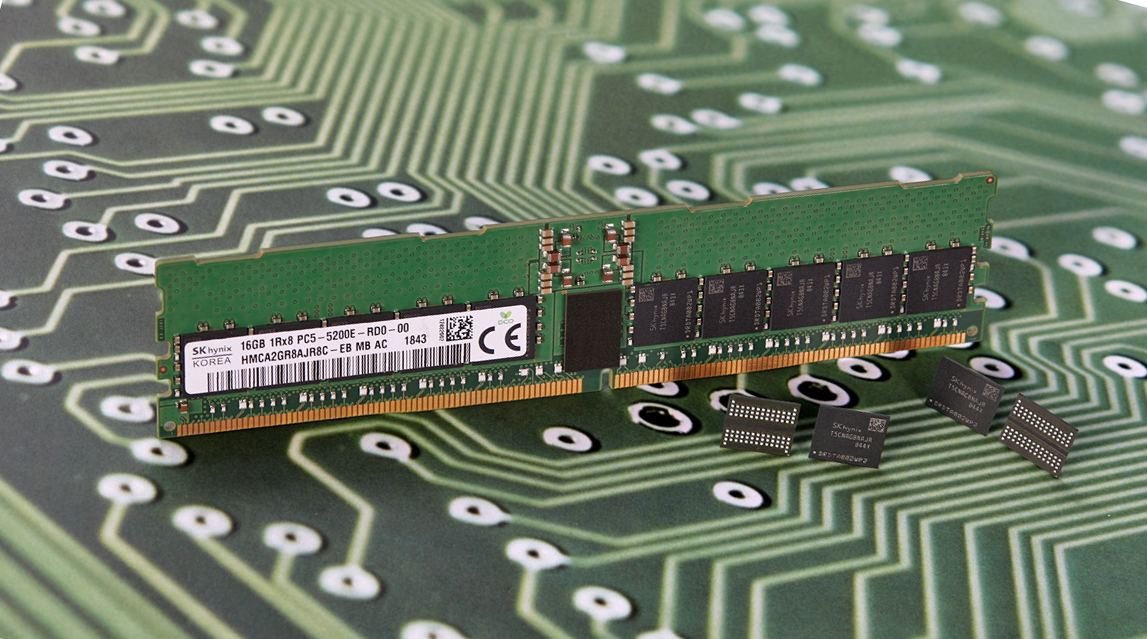

Zoveel mogelijk, zo snel mogelijk en zo goedkoop mogelijk: de eisen voor het werkgeheugen van een pc zijn simpel te verwoorden. De drie grote DRAM-fabrikanten Samsung, SK Hynix en Micron ontwikkelen hun chips en modules voortdurend op basis van die principes.

Tip

Krijg direct toegang tot alle beschikbare edities op je laptop, tablet of smartphone.

Om de paar jaar is er echter een nieuwe generatie nodig om de echt grote veranderingen door te kunnen voeren. Dit jaar worden de eerste pc’s met de vijfde generatie DDR-technologie (Double Data Rate) verwacht, oftewel DDR5-SDRAM. De smartphonevariant LPDDR5 is al in gebruik genomen.

Wisseling van de wacht

DDR5 vervangt het DDR4-geheugen dat sinds 2014 wordt gebruikt. Het nieuwe geheugen maakt vooral de weg vrij voor meer dan twee keer zo hoge snelheden bij data-overdracht. Dat verhoogt op zijn beurt de klokfrequentie van de geheugenbus.

Om ervoor te zorgen dat dit betrouwbaar werkt, zonder dat er vaak fouten worden gemaakt en/of het energieverbruik uit de hand loopt, zijn er tal van innovaties. DDR5-SDRAM zou ook het dubbele tot vier keer zo veel geheugencapaciteit vergeleken met de huidige RAM-modules mogelijk moeten make. Dat komt neer op modules met elk 64 GB en later zelfs 128 GB in plaats van de tot nu toe gebruikelijke limiet van 32 GB.

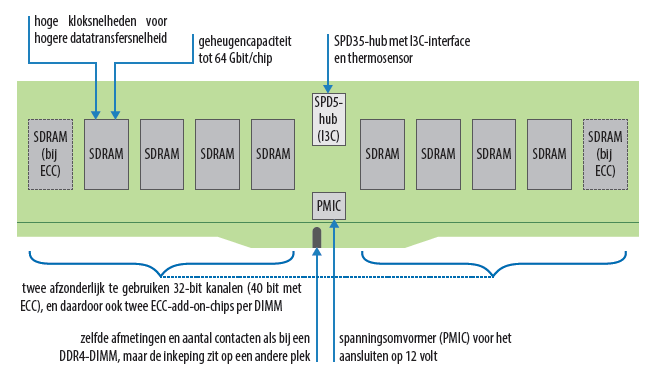

En er zijn enkele fundamenteel nieuwe functies, zoals het feit dat de standaard 64-bit geheugenbus ook kan worden gebruikt als twee 32-bit kanalen. Daardoor krijgen de vele cpu-cores van moderne processors efficiënter toegang tot het geheugen – maar wel op het rijtje af.

DDR5-geheugen: wijzigingen t.o.v. DDR4 Een geheugenmodule (DIMM) met DDR5-SDRAM lijkt aan de buitenkant vergelijkbaar met een DDR4-DIMM en verstuurt ook twee datapakketten per klokcyclus (Double Data Rate). Maar niet alleen de frequentie en de capaciteit nemen toe, er zijn ook tal van andere veranderingen.

Buitenkant

Dual Inline Memory Modules (DIMM’s) met DDR5-chips zijn echter nog nergens te koop en de specificaties van de JEDEC-industriecommissie zijn ook nog niet definitief. Belangrijke punten zijn echter al duidelijk. Zo zullen DDR5-DIMM’s qua uiterlijk nauwelijks verschillen van de DDR4-generatie. Ze hebben pcb’s van dezelfde grootte en 288 contacten. De inkeping zit echter op een andere plek, dus DDR5-DIMM’s passen niet in DDR4-slots.

De afmetingen van de kleinere Small Outline (SO) DIMM’s voor laptops blijven ook gelijk. Een DDR5-SODIMM zou echter 2 contacten meer hebben dan zijn voorganger (262 in plaats van 260). Bij laptops is er echter een trend van vast gesoldeerd geheugen, dat door de steeds plattere behuizingen niet meer te vervangen of aan te passen is.

Een positieve bijwerking is dat dit RAM hoger kan klokken dankzij korte lanes. Laptopfabrikanten vertrouwen vaak op low-power-chips zoals LPDDR4 en LPDDR4X, die zijn ontwikkeld voor smartphones en tablets.

Meer snelheid

De afkorting DDR staat voor Double Data Rate. De geheugenbus stuurt twee datapakketten per kloktik over. Bij DDR4-3200 is de klokfrequentie dus 1600 MHz (1,6 GHz) en gaan er 3,2 miljard overdrachten per seconde (3,2 GT/s) over de bus. Met 64 signaallijnen voor data (8 bytes per overdracht) komt dat uit op een maximale overdrachtssnelheid van 25,6 gigabyte per seconde (GB/s).

DDR5 klokt veel hoger dan DDR4. De eerste versie van de specificatie gaat tot DDR5-5200 – dat zou 41,6 GB/s zijn, 60 procent meer dan bij DDR4. Maar JEDEC denkt al aan DDR5-8400 (67,2 GB/s), dat is 2,6 keer de snelheid van DDR4-3200. Wanneer dergelijke modules beschikbaar gaan worden is nog onbekend. In het begin zijn de snelheidsvoordelen van nieuwe DDR-generaties vaak klein.

Het gaat daarbij niet over overgeklokt geheugen, het gaat hier alleen over JEDEC-conforme modules die zich nauwgezet aan tientallen parameters houden. Dat is nodig voor een betrouwbare werking en voor het door elkaar gebruiken van geheugenmodules van verschillende leveranciers. Overklokken verhoogt het energieverbruik en de kans op gegevensfouten aanzienlijk. Daar zit je bij servers echt niet op te wachten.

Maar sneller geheugen is juist erg belangrijk voor servers en supercomputers, en niet alleen om data te kunnen leveren aan het steeds groter wordende aantal cpu-cores. De I/O-datarates stijgen ook sterk door PCI Express 4.0 (PCIe 4.0) en de in 2021 verwachte opvolger PCIe 5.0.

Blijf op de hoogte van de nieuwste informatie en tips! Schrijf je in voor de nieuwsbrief:

De genoemde overdrachtssnelheden zijn allemaal theoretische maxima omdat de geheugenchips niet continu kunnen verzenden of ontvangen. Het adresseren duurt enige tijd en sommige vormen van toegang hebben latenties totdat de data uit de interne geheugencellen worden uitgelezen. Bovendien moeten DRAM-chips hun cellen met regelmatige tussenpozen verversen (refreshen) en kunnen ze niet tegelijkertijd gegevens leveren.

DDR5 biedt functies om die effecten te verminderen, zoals een efficiëntere aanpak en zogenaamde Same Bank Refresh. De DRAM-chips zouden echter gewoonweg te heet worden als ze continu op volledige snelheid hun werk moeten doen. Daarom zijn er altijd korte afkoelpauzes. DDR5 biedt ook nieuwe mogelijkheden voor een nauwkeurigere temperatuurbewaking met thermische sensoren op de DIMM.

Speedboost

De interne geheugenvelden van DRAM-chips kunnen niet zo makkelijk worden versneld als de geheugenbus, met name omdat de capaciteit van de chips naar verwachting zal toenemen. Hoe meer geheugencellen op een gedeelde lijn aangesloten zijn, des te langzamer het geheugenveld reageert. Het kan dus niet willekeurig snel worden gelezen of geschreven.

Om de externe overdrachtssnelheid van de DRAM-chips te verhogen, leest de chip echter meerdere zones van zijn interne geheugenvelden tegelijk uit en stuurt hij de data na elkaar naar zijn I/O-pinnen. Dat wordt prefetching genoemd. DDR4 werkt met acht parallelle toegangen (8N), DDR5 met 16 (16N). Bij DDR5 zijn de interne geheugenvelden echter verdeeld in kleinere gebieden, namelijk acht Bank Groups. Bij DDR4 zijn dat er vier (8BG/4BG).

Omdat een DDR5-chip per adresseringsproces altijd 16 bits intern leest (of schrijft), vindt de dataoverdracht op de geheugenbus ook plaats in sequenties van 16 opeenvolgende pakketten. Dat wordt Burst Length (BL) genoemd – in dit geval BL16. Met een 8 byte brede bus levert één enkel adresseringsproces dus 128 bytes aan data op. De caches van x86-processoren werken echter met een verdeling die slechts half zo groot is, hun zogenaamde Cache Line Lengte is 64 bytes – dat is het favoriete formaat van hun hapklare brokken. Dat is een van de redenen waarom DDR5 het mogelijk maakt om de 64-bit geheugenbus op te splitsen in twee afzonderlijk bruikbare 32-bit kanalen.

Bij DDR5 moeten de signaalfrequenties op de geheugenbus tot meer dan 4 GHz stijgen. Bij dergelijke hoge frequenties treden tal van fysieke effecten op die elektrische signalen verstoren en vervormen. Zelfs de uitbreidingssnelheid is een probleem: bij 4 GHz duurt een klokcyclus slechts 0,25 nanoseconde, in die tijd reist het signaal op een printplaat van het gebruikelijke FR4-materiaal minder dan 4 centimeter.

Een DIMM is drie keer zo lang en de signalen van de geheugencontroller (tegenwoordig in de processor ingebouwd) bereiken daarom niet alle SDRAM-chips op precies hetzelfde moment. Bovendien moeten de signalen meerdere storingspunten overwinnen: de soldeerverbindingen van de DRAM-chips, de contacten van de DIMM en de cpu-socket.

Een schat aan technische trucs optimaliseert de signaalkwaliteit. Zo passen de elektrische driverstappen in de SDRAM-chips en in de geheugencontroller zich met speciale trainingscycli aan elkaar aan. Op die manier compenseert het geheugensysteem ook schommelingen in temperatuur en voedingsspanning of veranderde contactweerstanden van slots. DDR5 maakt gebruik van meer gecompliceerde methoden zoals een Decision Feedback Equalizer (DFE) om het signaal te verbeteren, terwijl een Continuous Time Linear Equalizer (CTLE) voldoende was voor DDR4.

Een ander nieuw kenmerk van DDR5 is dat er niet meer alleen wordt getraind voor de datasignaallijnen (DQ), maar ook voor adressen en commando’s (Command and Address, CA). Voor dat laatste is er nu ook een schakelbare afsluiter (On-Die Termination, ODT) voor impedantiematching. Een andere truc is om bitpatronen op de geheugenbus te vermijden die bijzonder sterke interferentie zouden veroorzaken. Daar kunnen de DRAM-chips de datasignalen voor omkeren (Dynamic Bus Inversion, DBI).

Pietje preciezer

Bij DDR4 kan de geheugencontroller bij het schrijven van gegevens de checksums al berekenen, die hij aanvullend meestuurt en die de DRAM-chip vervolgens controleert. Als er afwijkingen zijn, vraagt het geheugen de data weer opnieuw op. Die Cyclic Redundancy Check (CRC) kost echter snelheid en werkt niet met alle DRAM-chips (alleen met x16- en x8-chips, niet met x4-chips). CRC is dan ook eerder een functie voor embedded systemen en niet voor desktops en servers. Nieuw in DDR5 is CRC voor leesoperaties.

Een beproefde techniek voor servers en workstations is ECC (Error Correction Code), waarbij de geheugencontroller redundante gegevens berekent en opslaat in extra DRAM-chips. De geheugenbus heeft ook extra lijnen nodig voor ECC, namelijk 72 in plaats van 64 voor 1 byte ECC per 8 bytes aan data. Bij DDR5 verandert dat omdat de 64-bit bus ook als twee 32-bit kanalen kan worden gebruikt. Er is een aparte ECC per kanaal, namelijk 1 byte per 4 bytes, en acht extra lijnen voor dat doel.

Een DDR5-ECC-DIMM gebruikt dus twee keer 40 datalijnen, in totaal 80 in plaats van 72. DDR5-ECC-DIMM’s hebben per rank één of twee chips meer dan DDR4-ECC-modules, dus 10 in plaats van 9 of 20 in plaats van 18. Dat verhoogt ook de mate van redundantie. Het is echter nog niet duidelijk of fabrikanten dat zullen gebruiken voor verbeterde correctiefuncties.

Al voor DDR4 was het de bedoeling dat de afzonderlijke SDRAM-chips ook intern gegevensfouten zouden kunnen corrigeren. De DDR5-specificatie biedt nu ook interne ECC. Of die technologie later in pc’s en laptops zal worden gebruikt of dat het gericht is op speciale toepassingen is echter nog onbekend.

- AI en cognitieve vaardigheden

- Werken met gestructureerde processen

- Gaat AI werknemers vervangen?

- c’t security-checklist 2026

DDR5 voor servers

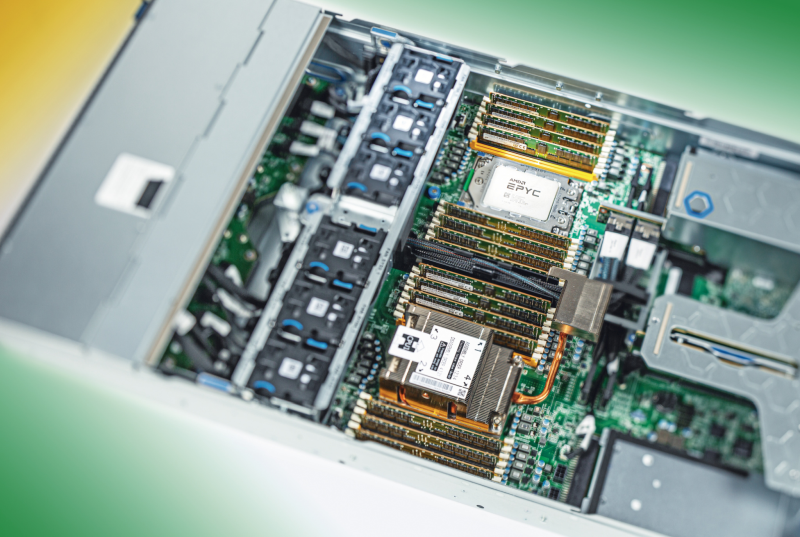

Het is nog onduidelijk in welke processorgeneratie van AMD, Intel, IBM en ARM het startsignaal voor DDR5-SDRAM zal worden gegeven. Er zijn enkele aanwijzingen dat de serverprocessors AMD Epyc Genoa (Zen 4) en Intel Xeon Sapphire Rapids in 2021 in staat zullen zijn om met DDR5 te overweg te kunnen. Misschien kunnen ze dan als alternatief in een DDR4-modus draaien.

Zo’n compatibiliteit is gebruikelijk bij nieuwe generaties RAM-geheugen, zodat moederborden nog steeds kunnen worden geproduceerd voor het oudere, in eerste instantie vaak goedkopere of beter beschikbare type geheugen.

Afhankelijk van de toepassing zijn verschillende DDR5-innovaties belangrijk voor servers. Voor virtualisatie en voor in-memory databases is aanzienlijk meer geheugen per cpu-socket een grote wens, terwijl AI-systemen en supercomputers de neiging hebben te profiteren van hogere overdrachtssnelheden.

De huidige serverprocessors zoals AMD Epyc Rome en Intel Xeon-SP hebben al zes of acht geheugenkanalen per cpu, de gangbare dual-processor machines hebben dus 12 of 16 geheugenkanalen met maximaal 32 DIMM-slots. Daar moeten meer dan 4000 signaallijnen voor op het moederbord worden gelegd. In plaats van nog meer geheugenkanalen per cpu zijn hogere overdrachtssnelheden per kanaal praktischer.

Bij de huidige DDR4-generatie zijn er LRDIMM’s voor servers met een maximale capaciteit van 256 GB. Daar kan een AMD Epyc 7002 er twee via elk van zijn acht kanalen van aansturen, dus 16 modules met een totale capaciteit van 4 TB. Bij een dual-socket server is momenteel 8 TB geheugen mogelijk. Met aankomende DDR5-systemen zou 8 TB per cpu (16 TB bij twee processors) mogelijk moeten zijn. Later zou dat weer kunnen verdubbelen.

I3C in plaats van I2C

Zelfs oudere DDR-geheugenmodules hebben elektronische specsheets die door het BIOS worden gelezen om de juiste parameters voor de klokfrequentie en latenties in de geheugencontroller in te stellen. Dat zogenaamde Serial Presence Detect (SPD) EEPROM is eigenlijk een flashgeheugenchip met een capaciteit van 128 of 256 bytes en gestandaardiseerde I2C-interface, ook wel geschreven als I2C.

Die afkorting staat voor Inter Integrated Circuit. Die interface uit de jaren 80 wordt in een pc ook wel System Management Bus (SMBus) genoemd. DDR5 schakelt nu over op de flexibelere en snellere I2C-opvolger I3C. De configuratiegegevens kunnen daarbij tot 1024 bytes bevatten.

Bovendien dient de SPD-chip niet meer alleen als configuratiegeheugen, maar verbindt hij ook andere componenten met de DIMM. Dat wordt aangegeven met de aanduiding SPD5 Hub. Die componenten omvatten nauwkeurig gespecificeerde temperatuursensoren, die al bij sommige SPD5-hubs ingebouwd zijn. Als de DIMM een eigen spanningsomvormer heeft, communiceert de hub ook met de PMIC (Power Management IC), die de omvormer aanstuurt.

DIMM’s met PMIC kunnen direct op 12 volt (servers) of 5 volt (pc’s) worden gebruikt. Dat vereenvoudigt aan de ene kant het ontwerp van de moederborden en bespaart kosten en ruimte, maar maakt ook het gebruik van bijvoorbeeld SDRAM-chips met verschillende bedrijfsspanningen mogelijk – bijvoorbeeld versies die zeer zuinig zijn.

| DDR5 brengt een hele reeks extra veranderingen met zich mee. Zo is bijvoorbeeld de overdracht van besturingscommando’s en adressen gewijzigd, zodat er minder lijnen nodig zijn. Aan de andere kant kan de geheugencontroller nu de twee ‘helften’ van een DIMM afzonderlijk aansturen. Sommige adresseringsprocessen bij DDR5 vereisen twee klokcycli, maar bij veel toegangsvarianten heeft dat echter geen zin omdat er door de langere bursts minder adressen verstuurd worden.

De toekomst

Enkele eerdere wijzigingen in geheugengeneraties, bijvoorbeeld van DDR2 naar DDR3, vielen in het begin tegen omdat de aanvankelijk beschikbare varianten van de nieuwe modules nauwelijks voordelen boden. Pas later kwamen er DIMM’s met significant hogere kloksnelheden, en ook de cpu-bouwers leerden bij en maakten beter gebruik van de nieuwe mogelijkheden.

De invloed van sneller RAM in pc’s en laptops wordt vaak echter overschat. Met typische desktopprogramma’s merk je daar bijna nooit wat van, vooral omdat steeds grotere caches in de processors vele benaderingen van het geheugen afvangen en dat is precies het doel. Sneller RAM heeft een bijzonder sterke invloed op de prestaties van gpu’s die in een processor geïntegreerd zijn, maar in de praktijk heb je daar niets aan, want die zijn nog steeds te sloom voor veeleisende games.

Overklok-experimenten met de Ryzen 3000 laten zien dat pc-games en sommige multithreaded-applicaties het meest profiteren van lagere RAM-latenties. Wat DDR5 in dat opzicht te bieden heeft, kan nog nauwelijks ingeschat worden. In eerste instantie is DDR5-RAM vooral belangrijk voor supercomputers, ongeacht of de toekomstige processors met 80 of meer cores de rekenkracht zelf zullen leveren of dat AI-versnellers met PCIe 5.0 enorme datatransfersnelheden zullen vereisen.

(informatie afkomstig uit het artikel van Christof Windeck en Alieke van Sommeren, c’t magazine 09/2020, p. 108)

Tip

Krijg direct toegang tot alle beschikbare edities op je laptop, tablet of smartphone.

Praat mee