Rowhammer, JackHammer en andere aanvallen op het RAM

Met zijn aanvalstactiek is Rowhammer (en de recente variant JackHammer) in staat de krachtigste softwarebescherming te overmeesteren door de eigenschappen van de hardware te manipuleren. De cpu-lekken Spectre, Meltdown en ZombieLoad gebruiken hetzelfde concept. Ze laten goed zien hoe security niet alleen gaat over software.

Lees verder na de advertentie

Zelfs experts werden verrast door de Rowhammer-aanvallen op het werkgeheugen van pc’s, servers en smartphones die vijf jaar geleden werden ontdekt. Dergelijke aanvallen omzeilen alle softwarematige beveiligingen tegen malware volledig. Aanvallers kunnen via Rowhammer zelfs uit een geïsoleerde sandbox breken, de opslag van een parallel draaiende virtuele machine wijzigen en zich uitgebreidere toegangsrechten toe-eigenen om zo allerlei code uit te voeren. Enkele Rowhammer varianten werken zelfs op afstand: zo kan bijvoorbeeld schadelijke JavaScript-code van een gemanipuleerde website die door de browser wordt uitgevoerd, zich toegang verschaffen tot allerlei gegevens in het werkgeheugen.

Rowhammer toont aan hoe kwetsbaarheden van hardwarecomponenten misbruikt kunnen worden om veilheidsmaatregelen van het besturingssysteem, de browser en toepassingen te omzeilen. Als zogenaamde Microarchitectural Side-Channel Attack (MASCAT) is Rowhammer een voorloper van Spectre, Meltdown en ZombieLoad, de veiligheidslekken die in veel processors zitten. Het is daarom ook niet toevallig dat Rowhammer-expert Daniel Gruss van de TU in Graz ook Spectre en Meltdown op het spoor kwam.

Kwetsbaar RAM-geheugen

Tip!

Slimme IP-camera’s met live toezicht en haarscherpe beveiliging!

Rowhammer manipuleert via software losse bits in DRAM-cellen in het werkgeheugen door fysieke zwakke plekken van de SDRAM-geheugenchip uit te buiten. Een Rowhammer-aanval voert doelgericht leesbenaderingen uit op specifieke geheugencellen (het zogenaamde ‘hammering’) om de inhoud van fysiek nabijgelegen geheugencellen (rows) te wijzigen. Dat werkt omdat de geheugencellen van SDRAM-chips extreem dicht op elkaar gepakt zitten, waardoor er elektrische interactie tussen buurcellen plaatsvindt. Dit is natuurlijk niet wenselijk, maar werd voorheen als onkritisch beschouwd.

Om preciezer te zijn: de inhoud van individuele cellen van een zogenaamd slachtoffer-adresbereik kan van 0 naar 1 worden gewijzigd, of andersom (bit flip). Dit is mogelijk via een proces dat zeer snel en herhaaldelijk de nabijgelegen (agressor-)geheugenbereiken benadert. De clou hierbij is dat de slachtoffer- en agressor-geheugenbereiken fysiek gezien vlak bij elkaar liggen, in elk geval op dezelfde SDRAM-chip. In de logische adresruimte kan het slachtoffer echter in het geheugenbereik van een ander proces zitten dan het agressor-proces. Op deze manier ontwijkt Rowhammer de scheiding tussen verschillende virtuele adresbereiken van parallel draaiende processen.

Gangbare besturingssystemen gaan uit van een beveiligingsmodel waarbij de geheugenbereiken veilig van elkaar gescheiden kunnen worden. Als dat niet zo was, zouden bijvoorbeeld wachtwoordbeheerders zinloos zijn omdat elk programma dat op dat moment actief is, de geheimen van andere programma’s zou kunnen uitlezen zodra je het masterwachtwoord invoert. Doordat Rowhammer deze geheugenscheiding uitschakelt, kan een aanval meerdere niveaus van de systeem-stack benaderen en veel van de gebruikelijke beveiligingsmechanismen omzeilen.

Rowhammer is complex, maar niet puur theorie. Project Zero, het veiligheidsteam van Google, publiceerde al in 2015 twee exploits waarmee op Linux-systemen met standaard geheugenmodules de rechten van gebruikers met beperkte rechten via Rowhammer konden worden uitgebreid. Sindsdien zijn er talloze andere Rowhammer varianten gepubliceerd die andere invalshoeken voor hun aanval gebruiken, andere processorarchitecturen aanvallen of de aanval efficiënter maken. Het recente JackHammer (dat FPGA-cpu platforms aanvalt) is daar een voorbeeld van.

DRAM-opbouw

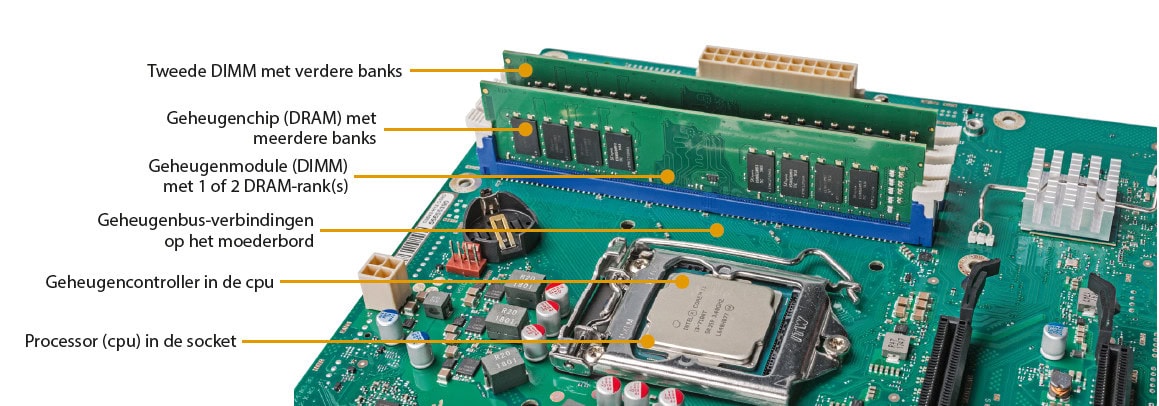

Om te begrijpen hoe een Rowhammer-aanval werkt, moet je een beeld hebben van de fysieke opbouw van geheugenmodules en van SDRAM-geheugenchips. Tot welke Double Data Rate (DDR) generatie de geheugenchips behoren – DDR3 of DDR4 – maakt niet uit. Het werkgeheugen van desktop-pc’s, notebooks, servers en smartphones is hiërarchisch onderverdeeld. De centrale geheugencontroller is bij actuele processors geïntegreerd in de chip van de processor. Hij maakt verbinding met een of meerdere DRAM-kanalen. Elk kanaal is aan de basis een bussysteem dat uit aansturing- en signaalverbindingen bestaat waar de SDRAM-chips mee zijn verbonden.

De individuele SDRAM’s kunnen op het moederbord gesoldeerd zitten, bijvoorbeeld bij smartphones en tablets. Bekender zijn de vervangbare geheugenmodules, de Dual-Inline Memory Modules ofwel DIMM’s voor desktop-pc’s, en Small Outline SO-DIMM’s voor notebooks. DIMM’s hebben 64 dataverbindingen, en elke afzonderlijke chip krijgt er daar 4, 8 of 16 van. Geheugenbenaderingen worden daarom altijd uitgevoerd op een groep van SDRAM-chips die gezamenlijk 64 dataverbindingen hebben. Zo’n groep wordt ‘rank’ genoemd. Die vormt na de geheugencontroller het volgende niveau in de geheugenhiërarchie. SO-DIMM’s en DIMM’s voor laptops en desktop-pc’s hebben elk een of twee ranks, registered DIMM’s voor servers kunnen er vier hebben.

In actuele DRAM-chips zitten enkele miljarden geheugencellen, bij een 8-gigabit-chip zijn het er bijvoorbeeld precies 8.589.934.592 (233). Om te zorgen dat de chip sneller werkt, zijn niet alle cellen in een enkel veld geplaatst, maar over verschillende banks verdeeld, die deels onafhankelijk van elkaar werken. Daardoor kan de geheugencontroller bijvoorbeeld voor een volgende benadering alvast het gewenste adres naar een bank sturen, terwijl hij nog op de eerder geadresseerde gegevens uit een andere bank wacht.

- AI en cognitieve vaardigheden

- Werken met gestructureerde processen

- Gaat AI werknemers vervangen?

- c’t security-checklist 2026

Elke bank is op zijn beurt weer in meerdere arrays onderverdeeld. Arrays zijn georganiseerd als een soort tabel, die bestaat uit rijen en kolommen van DRAM-cellen. Bij elk snijpunt van een rij met een kolom zit een enkele DRAM-cel, die één bit kan opslaan. Het uitlezen en schrijven van DRAM-cellen gaat per rij: elke array heeft zijn eigen set van schrijf-/leesversterkers, de zogenaamde sense amps. Een benaderingsopdracht op het adres van een bepaalde rij zorgt ervoor dat diens sense amps alle cellen uit de rij uitlezen.

Een DRAM-cel bestaat in wezen uit een ingangstransistor en een condensator. Die laatste vormt het eigenlijke opslagelement: als hij een lading heeft, representeert hij bijvoorbeeld de logische waarde 1, een condensator zonder lading correspondeert met 0. Een spanningsmeting kijkt wat de toestand van een cel is, waarbij een bepaalde grenswaarde het verschil tussen 0 en 1 registreert. Daaruit volgt dat de informatietoestand van een cel ook kan worden gewijzigd door ongewenste effecten die de ladingstoestand van een cel kunnen wijzigen.

Omdat de geheugencondensators zo klein zijn, is de lading van de cellen ook heel laag en zit in het femtofarad-bereik. Bovendien zijn de condensators niet ideaal geïsoleerd, maar zijn er meerdere effecten die voor een bepaalde mate van rest-geleidingsvermogen zorgen. Daardoor verliest een geladen condensator continu een klein beetje lading, waardoor het gevaar bestaat dat de informatie van 1 naar 0 schakelt. Omgekeerd kunnen ladingen in een ontladen condensator indringen en daarmee de waarde van 0 op 1 zetten. Zogenaamde refresh-cycli zijn speciale benaderingen die in vaste intervallen de toestand van elke individuele cel opfrissen. Daarbij lezen de sense amps een cel uit en schrijven dezelfde waarde weer terug. Vanwege deze dynamische verversing spreekt men ook wel over Dynamic RAM, ofwel DRAM. De refresh-intervallen duren tussen 32 en 64 milliseconden.

Opbouw van een DRAM-array (uitsnede)

Een DRAM-chip bestaat uit meerdere banks met elk meerdere arrays van geheugencellen. Deze zijn in rijen (rows) en kolommen (columns) aangebracht en met connectors verbonden. Alle cellen in een rij hangen aan een gedeelde word-line. Loodrecht daarop leidt elke bit-line naar een schrijf/lees-versterker (sense-amplifier). Die laatste leest alle cellen in een rij gelijktijdig uit. De kolom-decoder selecteert telkens de gewenste bits doordat hij de uitgangen van de sense-amps verbindt met de databus.

Schrijven en lezen

Het schrijven en lezen van informatie uit DRAM-cellen loopt via elektrische leidingen die met de rijen en kolommen van DRAM-cellen verbonden zijn. Naast elkaar gelegen cellen zijn dus elektrisch verbonden. Bovendien genereert het lezen en schrijven parasitaire effecten die de lading van de cellen beïnvloedt.

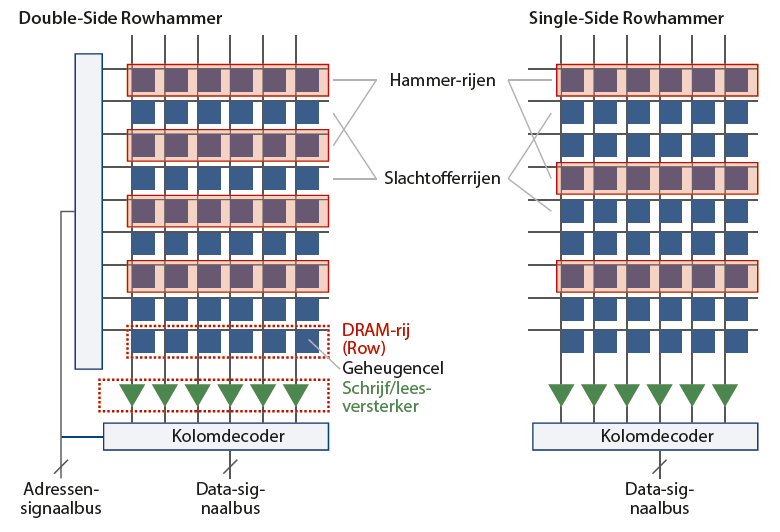

Niet alle DRAM-chips zijn even gevoelig voor Rowhammer-aanvallen. DRAM-cellen en hun verbindingen verschillen van chip tot chip. Elke grote DRAM-fabrikant heeft zijn eigen patenten, andere fabrieken, verschillende capaciteiten, diverse fabricagegeneraties, en ga zo maar door. Hammering beïnvloedt hele DRAM-rijen tegelijk: hoogfrequente leesbenaderingen op agressor-rijen triggeren bit-flips op naastgelegen slachtoffercellen in dezelfde bank. Daarbij wordt er verschil gemaakt tussen single-sided Rowhammer (SSRH) en double-sided Rowhammer (DSRH). SSRH bewerkt per slachtoffer-rij hooguit één naastgelegen agressorrij. DSRH valt per slachtoffer-rij beide naastgelegen rijen aan.

Experimenten van Google Project Zero hebben aangetoond dat DSRH meer bit-flips in de slachtoffer-rij genereert en bij relatief ongevoelige DRAM-modules de enige mogelijkheid was om bit-flips binnen een bruikbaar tijdsbestek te genereren.

Om überhaupt doelgericht op een bepaalde DRAM-rij te kunnen hameren, moet malware de geheugenhiërarchie en adresseringsschema plus meerdere virtualisatieniveaus overwinnen. Een proces dat onder een modern besturingssysteem draait, ontvangt van diens geheugenbeheer alleen maar virtuele adressen. Deze worden bijzonder complex afgebeeld op de fysieke adressen van de laatst gebruikte DRAM-geheugencellen.

Dat begint met de fysieke constructie van de SDRAM-bouwelementen en de gebruikte DIMM’s. Het BIOS stelt de geheugenranks die het aantreft samen tot adresblokken en houdt rekening met configuratieopties van de BIOS-setup, zoals kanaalbundeling. Als er een hypervisor is, gebruikt deze hardware-functies van de processor zoals second-level address translation (SLAT), wat dient om de beschikbare adresruimte dynamisch in blokken op te delen voor meerdere virtuele machines. Daarboven zit het virtuele geheugenbeheer van het desbetreffende besturingssysteem.

Vanuit de aanvaller vormen ook de verschillende buffers in de RAM-hiërarchie een uitdaging. Het systeem probeert normaliter een benaderingscommando op een geheugenadres in het cachegeheugen aan te sturen, c.q. in meerdere caches: L1-, L2- en L3-cache. Als een gewenst stukje data in de cache zit, is er sprake van een cache hit. Rowhammer moet er dan ook voor zorgen dat er juist databenaderingen tot het RAM volgen die de caches omzeilen oftewel: cache-miss.

Single- en double-sided Rowhammer

Bij Double-Side Rowhammer (DSRH) zit direct aan weerszijden van elke slachtoffer-rij een agressor-rij. Bij Single-Sided Rowhammer (SSRH) probeert maar één naastgelegen agressor-rij bit-flips te genereren bij een naastgelegen slachtoffer-rij.

Rowhammer vereisten

Om een Rowhammer-exploit te maken, moet de programmeur drie problemen oplossen. Allereerst moet het lukken de hoogfrequente lees-benaderingen direct op het DRAM uit te voeren, zonder dat deze in de cache terechtkomen. Er moeten twee logische geheugenadressen opgespoord worden die naar twee DRAM-rijen van dezelfde bank verwijzen en moet er in het geval van een double-sided Rowhammer een derde slachtoffer-rij opgespoord worden. Ten slotte moet het lukken slachtoffer-rijen te gebruiken die binnen een virtueel geheugenbereik zitten met datastructuren die met de beveiliging te maken hebben.

Om het cachegeheugen te omzeilen gebruikten de eerste Rowhammer-onderzoekers de processorinstructie CLFLUSH, die het cachegeheugen leegmaakt waardoor de eerstvolgende leesbenadering direct in het DRAM terechtkomt. Er zijn echter platforms, bijvoorbeeld systemen met ARM-chips, waar gebruikers of processen zonder voldoende rechten zulke instructies niet mogen gebruiken. Daarvoor werd een strategie uitgedacht om het cachegeheugen snel met foute waarden te vullen waarbij door het volle cachegeheugen de opvolgende leesbenadering een cache-miss genereert, en zo het DRAM direct aanspreekt. Alternatieve strategieën gebruiken instructies die helemaal niet in het cachegeheugen terechtkomen of die met DMA-benaderingen werken om de tussenopslag te verhinderen.

Het is ingewikkelder om de virtuele adressen van geschikte agressor- en slachtoffer-rijen te berekenen. Dat gaat hooguit enigszins eenvoudig wanneer de zogenaamde mapping van logische naar fysieke adressen precies kan worden achterhaald, bijvoorbeeld uit de documentatie van het besturingssysteem, cpu, BIOS en geheugenmodules. Zoals gezegd verschilt de mapping mogelijk al bij geheugenmodules die stammen uit verschillende productieseries van dezelfde fabrikant. Intussen worden al de eerste methoden ontwikkeld om de mapping via software te automatiseren. Een methode is het meten van de minimale tijdsverschillen tussen benaderingen van opgeslagen waarden. Cache-hits zijn duidelijk sneller dan cache-misses. Die laatste ‘verbruiken’ namelijk meer cpu-cycli dan een hit, en software herkent de tijdsverschillen. Bovendien buffert de cache de gegevens uit RAM in specifieke brokjes. Met deze informatie, en successievelijke benaderingen op adresbereiken, kan malware de mapping tussen logische en fysieke adressen achterhalen. Dat duurt wel even.

Onlangs werd de zogeheten ‘spoiler’-procedure voorgesteld, waarmee een proces zonder beheerdersrechten toch snel kan mappen [3]. Spoiler gebruikt de data-afhankelijkheid van het speculatief laden en opslaan in de Memory Order Buffer voor het identificeren van samenhangende fysieke geheugenbereiken.

Er zijn verschillende concepten om na het mappen adresbereiken te vinden met veiligheidsrelevante datastructuren. Een van die concepten is het onderzoeken van Page Table Entries (PTE). Deze bevatten naast de mapping tussen logische en fysieke adressen ook toegangsrechten op geheugenbereiken.

Indien een virtueel adresbereik is geïdentificeerd dat bruikbare doelwitten bevat, moet de malware dat koppelen aan het fysieke adres van een geschikte slachtoffer-rij. De RAM-adressen van datastructuren kunnen verschoven worden via procedures genaamd memory spraying – ook wel bekend als heap spraying – en memory grooming. Deze procedures worden ook bij andere aanvallen ingezet.

Kwetsbare DRAM’s

De eerste versies van Rowhammer richtten zich vooral op DDR3-geheugenmodules. Rond 85 procent van de geteste DDR3-DIMM’s van drie verschillende fabrikanten was kwetsbaar. Het team van Google onderzocht DDR3-modules van vijf fabrikanten in 29 algemeen verkrijgbare laptops. Bij 15 daarvan waren de bit-flips succesvol. In 2016 toonden onderzoekers van de TU Graz aan dat ook DDR4-SDRAM kwetsbaar was voor Rowhammer. Dat geldt in principe ook voor low-power (LP)DDR-SDRAM dat in smartphones zit.

In eerste instantie gingen experts er vanuit dat de correctiefunctie voor bitfouten, de Error Correction Code (ECC) die in het RAM van de meeste servers zit, die systemen tegen Rowhammer zou beschermen. Dit was echter niet zo. Om dat uit te leggen, moet je iets dieper in het principe achter de ECC-techniek duiken. De meest gangbare ECC-techniek herkent en corrigeert een enkele bitfout per 64-bits-woordlengte en is ook in staat om twee-bit-fouten te herkennen, hoewel deze tot een crash leiden. Drie of meer gelijktijdige bitfouten binnen een woord kan de ECC-techniek niet herkennen.

Experts vermoedden dat Rowhammer met grote waarschijnlijkheid allereerst 1- en 2-bitfouten genereert voordat meerdere bits tegelijkertijd flippen. Deze fouten zouden echter door ECC worden afgevangen. Onderzoekers van de Vrije Universiteit Amsterdam gingen er echter van uit dat Rowhammer drie of meer bit-flips kan genereren zonder eerst de foutcorrectie te activeren. Daarvoor emuleerden de onderzoekers een ECC-algoritme en vonden bit-flip-patronen waarmee ze de foutcorrectie konden foppen. Deze veranderde bits konden ze in het verdere verloop gebruiken om veiligheidskritische datastructuren te manipuleren. ECC-RAM beschermt weliswaar niet tegen Rowhammer-aanvallen, maar maakt ze wel een stuk moeilijker.

Aanvalsvectoren

De eerste Rowhammer-pogingen werden ondernomen op pc’s en servers met Intel-x86 en x86-64-processors, met name omdat daar ook via processen met beperkte rechten de caches met het CLFLUSH-commando kunnen worden gewist. Later verscheen er een JavaScript-versie van Rowhammer zonder CLFLUSH, die geheel geautomatiseerd in een browser kan draaien.

In 2016 werd aangetoond hoe een aanvaller via Rowhammer vanuit een virtuele machine een OpenSSH-toepassing aanpakte die in een andere virtuele machine draaide en op die manier de public-key-authenticatie wist te omzeilen. De exploit ‘Drammer’ pakt via Rowhammer systems-on-chip (SoC) met ARM-processors aan die in smartphones en routers zitten. Bovendien zijn er de varianten Nethammer en Throwhammer, die Rowhammer-aanvallen via netwerken kunnen uitvoeren.

Ondanks de diverse varianten van Rowhammer zijn tot op heden nog geen praktijkgevallen van aanvallen bekend. Vermoedelijk komt dit enerzijds door de relatief ingrijpende technische vereisten voor een dergelijke aanval en anderzijds omdat er over het algemeen voor criminelen genoeg andere en veel eenvoudigere manieren zijn om potentieel interessante doelwitten aan te vallen. Het is echter net zo min mogelijk om aan te tonen dat Rowhammer niet al ergens actief wordt toegepast, bijvoorbeeld voor een doelgerichte (spearhead-)aanval door geheime diensten om Advanced Persistent Threats (APT’s) te verstoppen in de computers van geheime organisaties.

Rowhammer bescherming

Volgens actuele inschattingen zou het Rowhammer-risico alleen weggenomen kunnen worden door de hardware van geheugencontrollers en geheugenchips te wijzigen. Voor bestaande systemen is dit geen realistische oplossing, hooguit voor toekomstige apparaten. Tot dan zijn softwarematige afweersystemen de enige oplossing. Zo zou je dubieuze programma’s niet zoals gebruikelijk kunnen laten uitvoeren, maar eerst statisch kunnen analyseren om te zoeken naar verdachte patronen van geheugenaanvallen.

Een andere insteek zijn de performance-counters van moderne processors. Bij een actieve Rowhammer-aanval zou een performance-counter hoge waarden registreren, waaraan je een aanval zou kunnen herkennen. Er bestaat een Rowhammer afweerstrategie die Anvil heet. Als de miss-rate van de cache een bepaalde drempelwaarde overschrijdt, voert Anvil zelf refresh-benaderingen op het DRAM uit. De benaderingen verhinderen dat er bits worden geflipt. Als een cel volledig geladen of geheel leeg is, dan daalt de kans dat zijn toestand kan worden geflipt.

Een Rowhammer-aanval kan ook verijdeld worden door de directe bewaking van DRAM-benaderingen, omdat Rowhammer met typische benaderingspatronen werkt: hoogfrequente aanvallen op bepaalde adresbereiken.

Enkele experts zijn procedures aan het ontwikkelen om de adresbereiken van het geheugen voor users en die van de kernel fysiek gezien zo ver mogelijk van elkaar te plaatsen, bijvoorbeeld in afzonderlijke DRAM-banks. Door de userpages en de kernelpages van elkaar te isoleren, zou het niet meer mogelijk zijn om toegangsrechten via bit-flips te veranderen. Ten slotte is er nog het idee om het ‘geheugenverbruik’ van processen te bewaken. Daarbij wordt in de gaten gehouden of er via het eerder genoemde heap-spraying in veiligheidskritische datastructuren een buitenproportioneel groot aantal adressen in de virtuele adresruimte aan het verschuiven is.

Volgens Yoongu Kim zijn de hardwarefabrikanten al sinds 2012 op de hoogte van het Rowhammer-concept. De eerste ideeën voor tegenmaatregelen werden pas in 2014 gepubliceerd. Een daarvan is om de refresh-intervallen korter te maken. Kim constateerde echter dat de refresh-rate met een factor acht verhoogd zou moeten worden om bit-flips onmogelijk te maken. Daardoor zou de maximaal bruikbare datatransferrate van het werkgeheugen weer dalen omdat er minder tijd overblijft voor benaderingen. Bovendien stijgt dan het energieverbruik van het werkgeheugen wat op zijn beurt weer een negatief effect heeft op de accuduur van laptops en met name smartphones.

De actuele generatie LPDDR4-geheugen bevat inmiddels twee functies die een Rowhammer-aanval op z’n minst moeilijker maken: Target Row Refresh (TRR) en Maximum Activation Count (MAC). Bij TRR heeft een LPDDR4-chip voor elke DRAM-rij een teller. Die wordt bij elke benadering op een van beide direct naastgelegen rijen verhoogd. Zodra een teller een drempelwaarde overschrijdt, worden de naastgelegen rijen gerefresht. Ook MAC houdt een drempelwaarde bij die monitort hoe vaak een DRAM-rij mag worden uitgelezen voordat de naastgelegen rijen automatisch worden ververst.

Conclusie

Rowhammer-aanvallen zijn fascinerend: ze weten via de hardware allerlei beveiligingsmaatregelen van apps, besturingssystemen en firmware te omzeilen. Gelukkig is een Rowhammer-aanval zeer ingewikkeld en ingrijpend, omdat deze rekening moet houden met de individuele eigenschappen van de aanwezige hardware. Daardoor spelen Rowhammer-aanvallen in de praktijk vermoedelijk nog geen rol.

Toekomstige verbeteringen (zoals hier beschreven) en automatisering zouden daar echter verandering in kunnen brengen en Rowhammer aantrekkelijk kunnen maken, net zoals de angst bestaat dat dit voor aanvallen met Spectre het geval is.

Rowhammer laat zien dat IT-veiligheid een holistische denkwijze behoeft: een betrouwbare beveiliging moet het systeem als geheel beschouwen, en niet alleen als losse onderdelen zien.

(André Schaller en Daniel Dupré, c’t magazine) Dr. André Schaller was lid van het onderzoeksteam Security Engineering aan de TU Darmstadt, dat deel uitmaakt van het veiligheidssamenwerkingsverband CYSEC

- AI en cognitieve vaardigheden

- Werken met gestructureerde processen

- Gaat AI werknemers vervangen?

- c’t security-checklist 2026

Tip

Krijg direct toegang tot alle beschikbare edities op je laptop, tablet of smartphone.

Praat mee