AMD Epyc 7003 Milan en Intel Xeon-SP Gen 3 Ice Lake voor servers

Inleiding

Lees verder na de advertentie

We hebben Intels eerste Xeon-serverprocessors met 10nm-technologie vergeleken met de derde generatie Epyc-processors van AMD. Lukt het Intel om AMD weer voorbij te streven?

Hoewel de eerste AMD Epyc meer dan drie jaar geleden verscheen en aan zijn derde generatie (Milan) toe is, blijven de Xeons van Intel de markt voor serverprocessors domineren. De Xeon Scalable Processors (Xeon-SP) kregen echter een reality-check: de prijzen en de verkoop daalden in de tussentijd aanzienlijk. De Xeon-SP-generatie Ice Lake met 10-nanometer technologie (die eigenlijk al jaren eerder gepland was) zou de grote achterstand op de 64-core Epyc nu moeten inlopen.

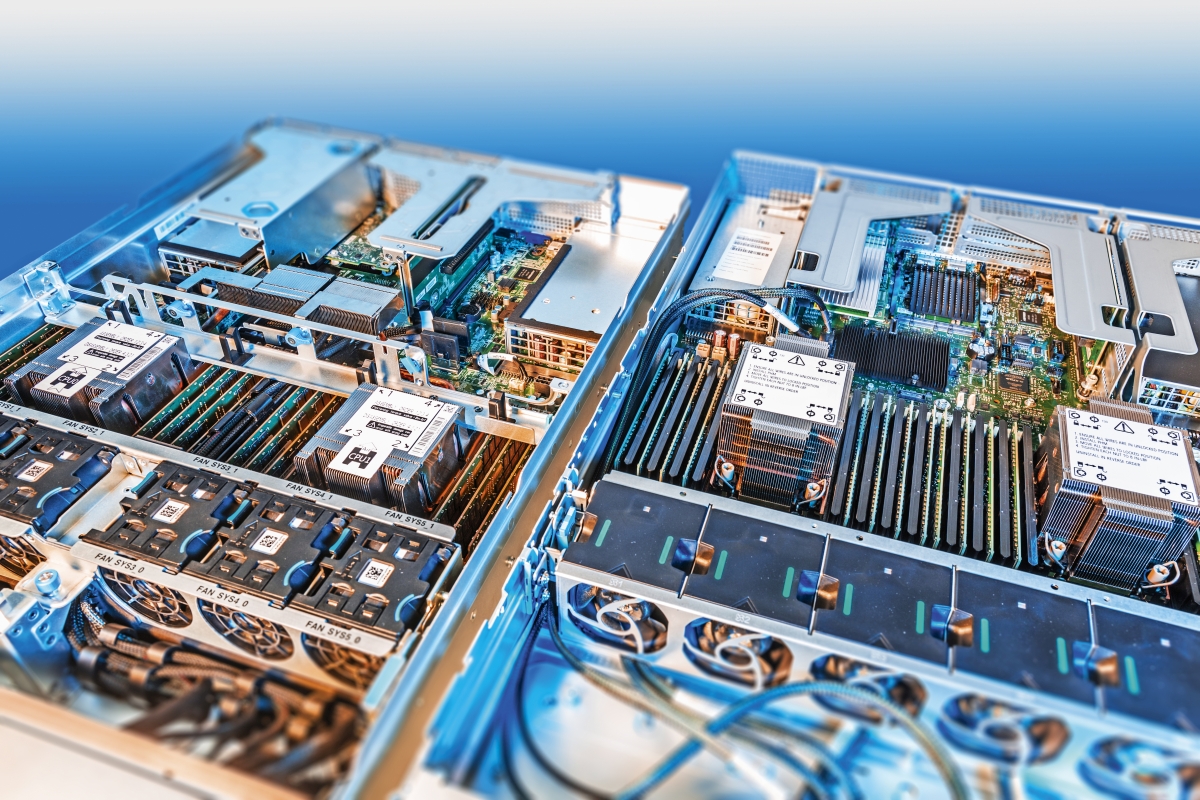

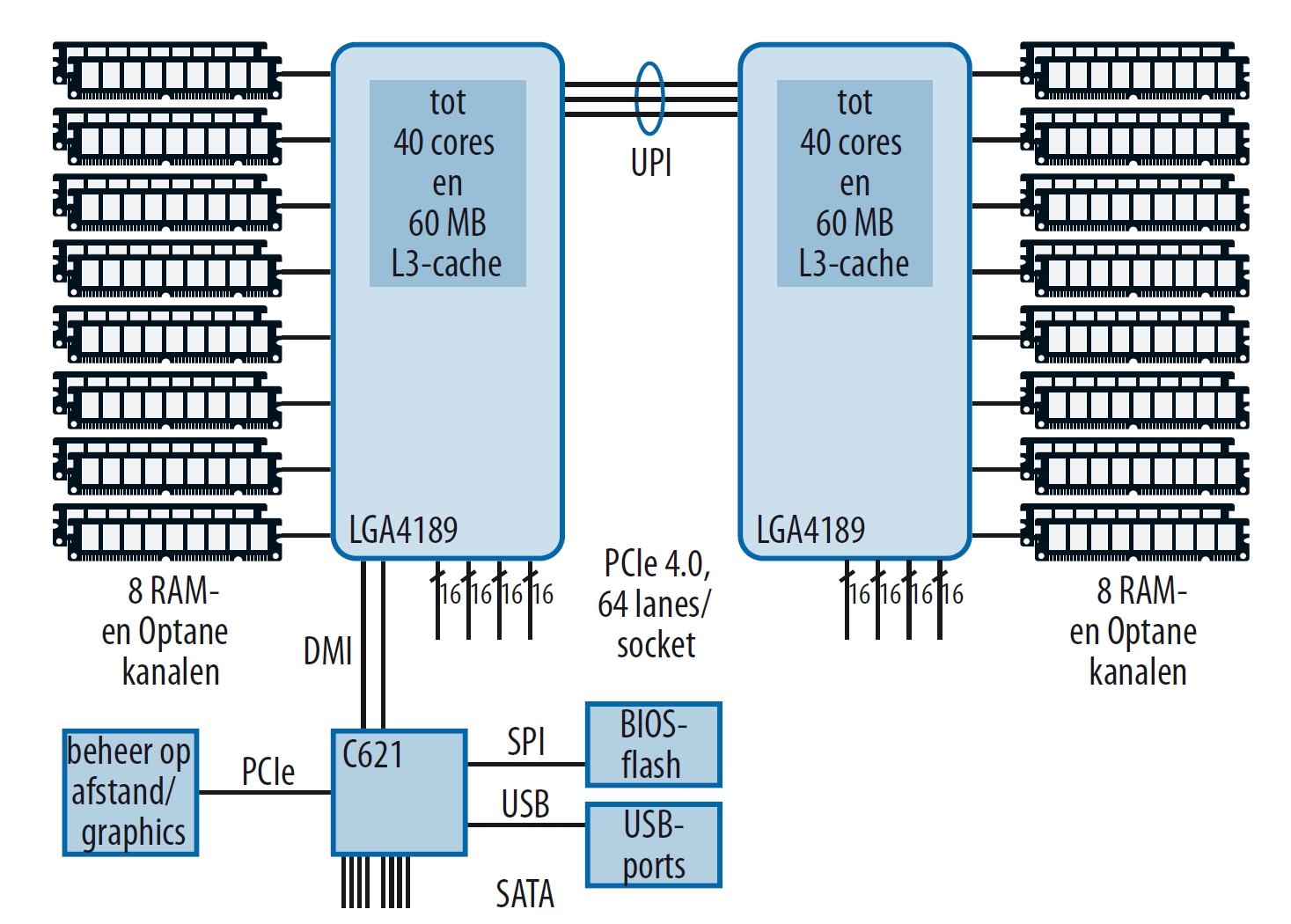

De nieuwe Xeons hebben tot 40 in plaats van slechts 28 cpu-cores en komen op gelijke hoogte met de Epycs op het gebied van de PCI Express-standaard (met PCIe 4.0 in plaats van 3.0) en RAM (met acht in plaats van zes geheugenkanalen). AMD heeft de derde generatie Epyc verbeterd met Zen 3-microarchitectuur. Aangezien serverfabrikanten zoals Gigabyte veelal beide platforms in hun assortiment hebben, bekijken wij de rivalen op hun bijzondere eigenschappen.

Tip

Krijg direct toegang tot alle beschikbare edities op je laptop, tablet of smartphone.

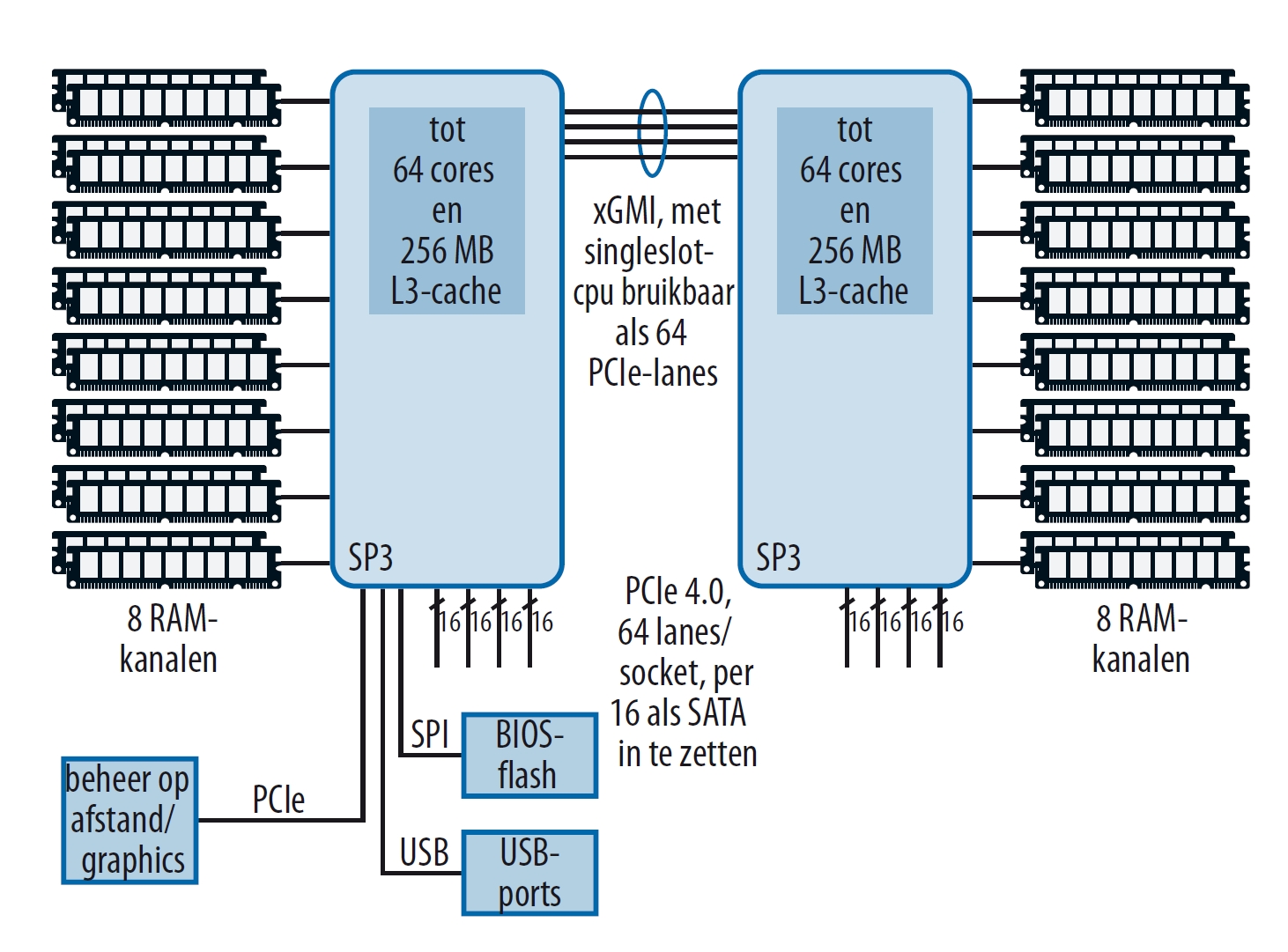

Merkbare optimalisaties

Bij Epyc is de stap van Zen 2 (7002, Rome) naar Zen 3 niet erg groot, maar wel significant. Epyc 7003-cpu’s draaien in dezelfde servers en moederborden als hun voorgangers, mits de betreffende fabrikant een BIOS- update levert. Daardoor blijven de versie SP3 (zie de tabel verderop) en acht geheugenkanalen en 128 PCIe 4.0- lanes per cpu bestaan, waarvan de helft wordt gebruikt om de tweede processor aan te sluiten in een dual-socket (2S) systeem. Het aantal cores en de cache-capaciteit zijn ook hetzelfde gebleven.

AMD heeft echter de rekenkernen en de structuur van de zogenaamde Core Complexes (CCX) slim geoptimaliseerd, net als bij de Ryzen 5000, die al in de herfst van 2020 geïntroduceerd werd. In vergelijking met de voorganger heeft AMD vooral de latentie verminderd, onder meer door een betere aansluiting van de Level 3-cache (L3), die nog steeds 32 MB groot is en waarvan de volledige capaciteit nu ook rechtstreeks door een enkele core kan worden aangesproken. De jump-prediction en geheugendoorvoer zijn ook verbeterd. Afhankelijk van de code verwerkt een Zen 3-core ongeveer 10 tot 20 procent meer instructies per cyclus (IPC) dan de cores in de Zen 2. AMD komt ook met meer Epyc-versies met 240 en 280 watt Thermal Design Power (TDP). Die klokken gemiddeld hoger dan hun 225-watt voorgangers, mits het betreffende servermoederbord voldoende power levert en de koeling meewerkt. AMD biedt ook enkele Epyc F-versies met minder cores, maar met een bijzonder hoge turbokloksnelheid en maximale cache-uitbreiding. Die zijn zeer geschikt voor software waarbij je licenties betaalt per cpu-core, en voor toepassingen waarbij de laagste latency belangrijk is.

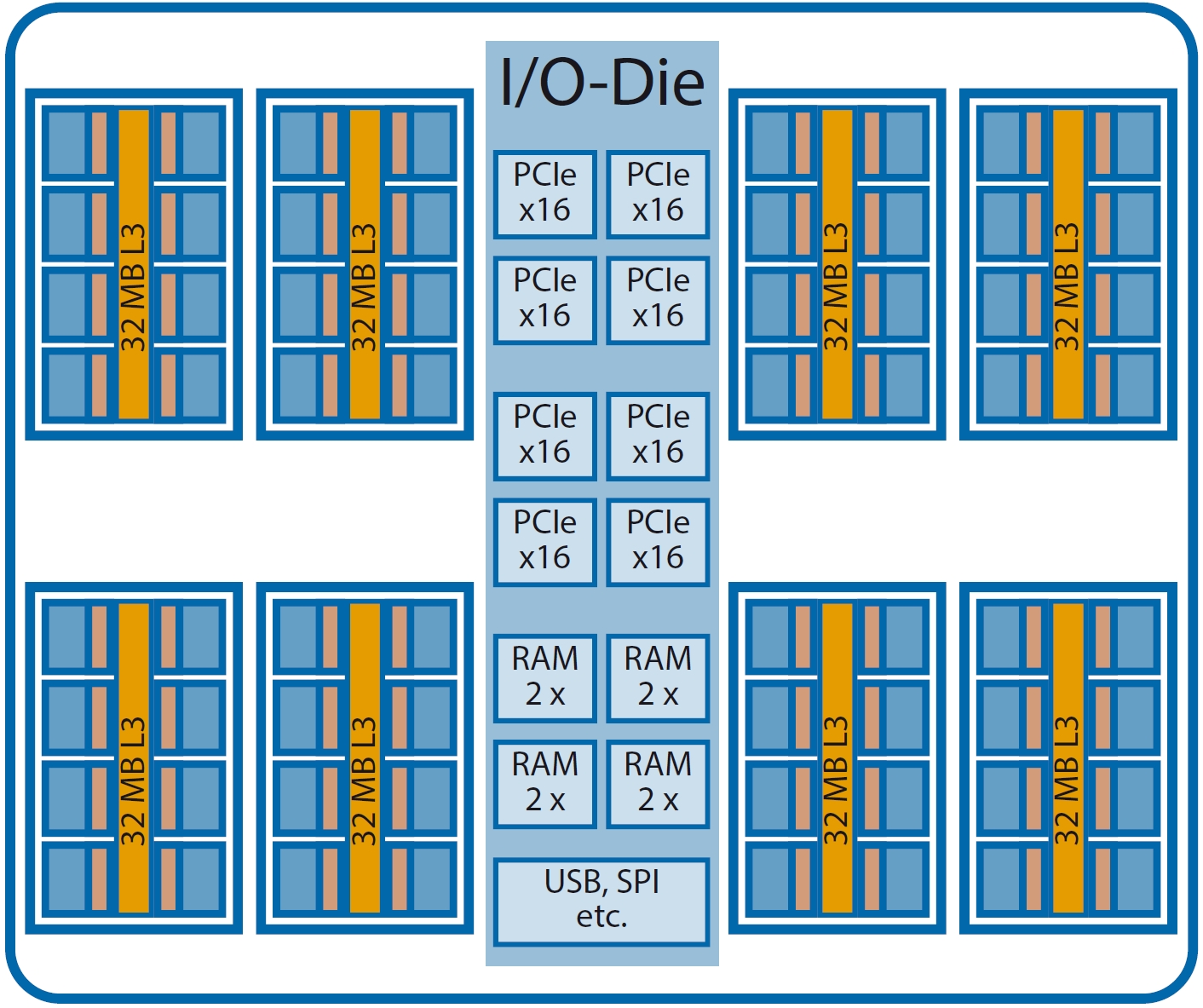

AMD blijft vertrouwen op een chiplet-ontwerp, waarbij verschillende silicium-dies in één processor worden gecombineerd. Het blijft bij acht CCX-dies (CCD’s) met elk acht cpu-cores, die de contractfabrikant TSMC produceert met 7nm-technologie. De aansluiting van RAM, PCI Express, SATA, USB en andere I/O functies wordt geregeld door de I/O-die, die nog steeds wordt geproduceerd door Globalfoundries met de oude 12nm-technologie. Voor de I/O-dies waren er slechts kleine updates voor beveiligingsfuncties.

Xeon-update

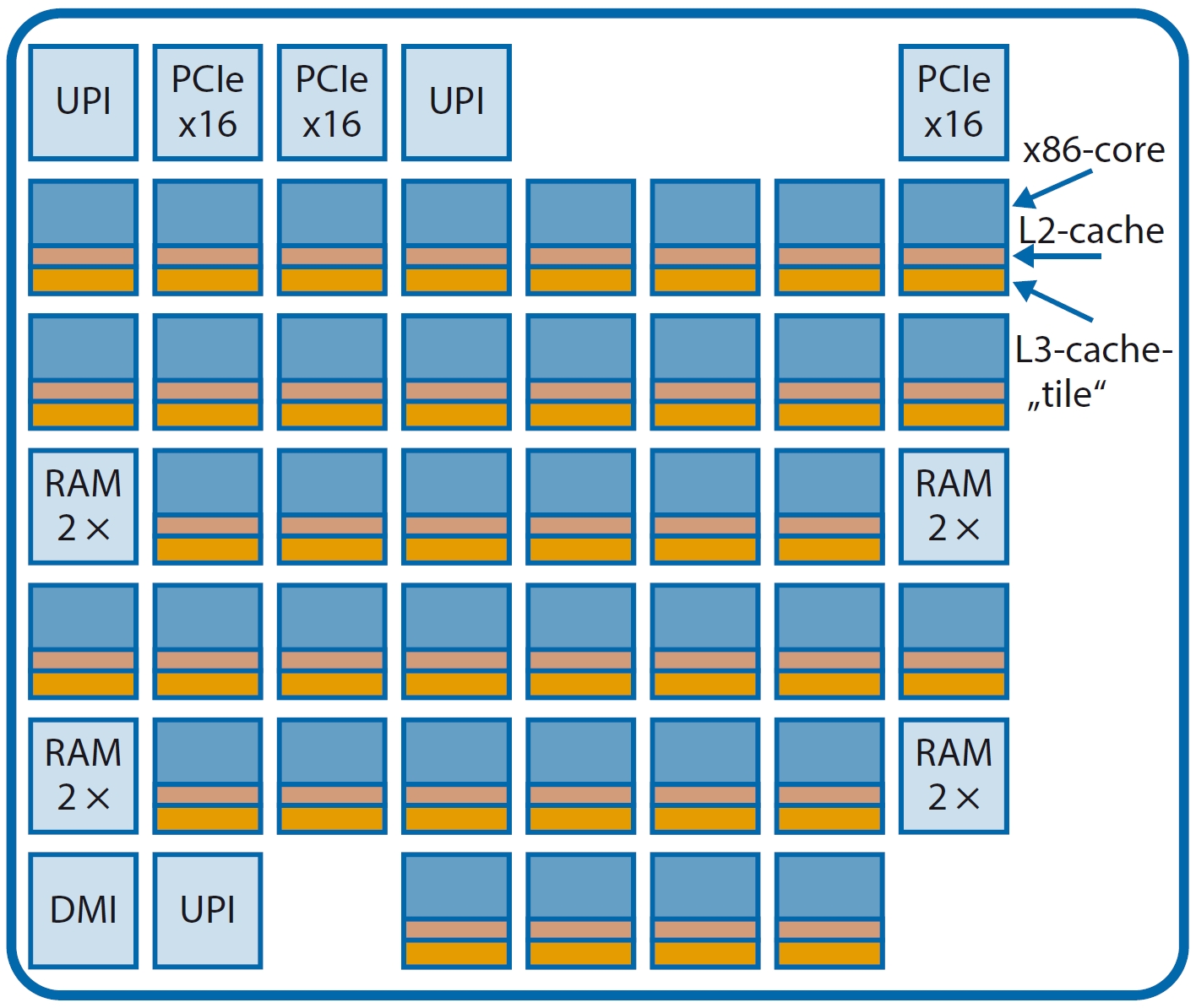

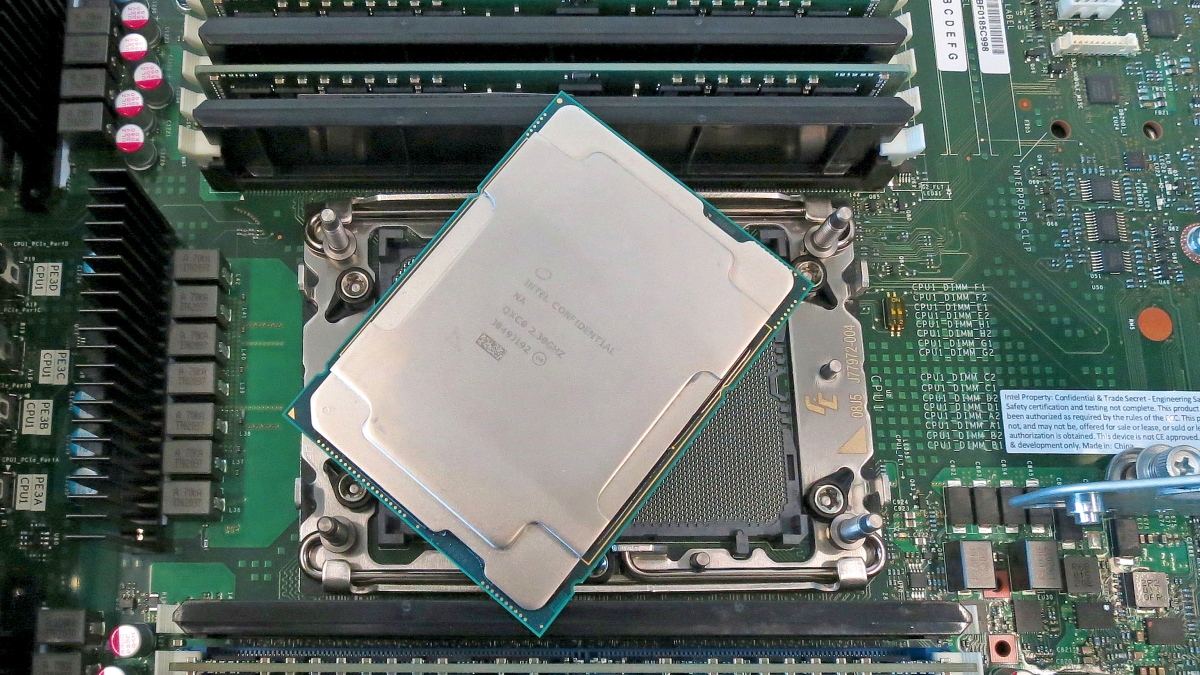

Vergeleken met zijn directe voorganger Cascade Lake, heeft de Ice Lake Xeon bijna revolutionaire vernieuwingen. Intel schakelt niet alleen over van 14- naar 10nm-productie, waardoor 42 procent meer kernen in de processor kunnen, maar er zijn ook volledig herziene Sunny Cove-rekenkernen met nieuwe functies, PCI Express 4.0 in plaats van PCIe 3.0, 64 in plaats van 48 PCIe-lanes en acht in plaats van zes geheugenkanalen. De vele extra aansluitingen vereisen de nieuwe LGA4189-socket, dus ook nieuwe moederborden. Bovendien noteert AMD 913 dollar op de prijslijst voor de goedkoopste Milan-Epyc 7313P (16 cores), terwijl Intels Xeon Silver 4309Y (8 cores) begint bij 500 dollar – ook iets wat we niet eerder zagen.

Intel belooft voor Sunny Cove gemiddeld 20 procent meer rekenkracht per klokcyclus dan voor Cascade Lake. Ice Lake Xeons blijven echter ook ongeveer 20 procent onder de turbofrequenties van Cascade Lake (maximaal 3,7 in plaats van maximaal 4,5 GHz). Maar omdat er nu veel meer cores zijn (overigens ook meer cores per euro dan bij de voorgangers), neemt de rekenkracht per fysieke processor aanzienlijk toe.

Dat de Ice Lake-technologie niet de hoge frequenties van de voorgangers haalt, bleek al in 2019 bij de mobiele processoren van de tiende Core i-generatie. Intussen is Intel overgestapt op de elfde generatie Tiger Lake met verder geoptimaliseerde Willow Cove-cores, die meer dan 4,5 GHz halen. Vergelijkbare cores zullen waarschijnlijk ook worden gebruikt in de voor 2022 aangekondigde Sapphire Rapids-generatie Xeons, die ook DDR5-RAM en PCI Express 5.0 ondersteunen en opnieuw een nieuwe cpu-socket vereisen – vermoedelijk LGA4677.

De huidige Ice Lake Xeons van de derde generatie (Gen 3) zijn dus een soort tussengeneratie. Dait komt ook tot uiting in de verwarrende onderverdeling in marktsegmenten: er waren eerder al Gen 3 Xeon SP’s. Die Cooper Lake-types zijn nog afkomstig van de 14nm-productie en zijn bedoeld voor servers met vier en meer processors. Ze zijn op de typelijst te herkennen aan een achteraan toegevoegde H, bijvoorbeeld Xeon Platinum 8380H in plaats van 8380. Omgekeerd zijn de nieuwe Ice Lake Xeon SP’s (net als de Epycs) gericht op servers met één of twee cpu-sockets en zijn er net als bij de Epycs goedkopere versies alleen voor single-slot gebruik (U-types, bij Epyc P-types).

Speciale functies

De Epyc en Xeon-SP bieden elk exclusieve functies voor specifieke doelen. De Epyc biedt bijvoorbeeld Secure Encrypted Virtualization (SEV) om de afzonderlijke geheugenadresgebieden van parallel draaiende virtuele machines verschillend te versleutelen. Enerzijds dient dat voor zogenaamd Confident Computing in de cloud, waarbij zelfs een beheerder met rootrechten de inhoud van het geheugen niet kan achterhalen. Anderzijds laat SEV side-channel-aanvallen zoals Spectre, waarbij malware in de ene virtuele machine probeert data van een andere te stelen, mislukken. SEV kan onder meer worden gebruikt met de VMware ESXi-hypervisor, en in de toekomst zelfs in de Encrypted State-versie (SEV-ES), die zelfs voorkomt dat de hypervisor (aka VM Monitor) in het geheugen van de virtuele machine kan kijken.

De Ice Lake-Xeon is alleen in staat tot de transparante volledige geheugenversleuteling Total Memory Encryption (TME), waarbij al het geheugen met dezelfde sleutel wordt beschermd. Intel had oorspronkelijk ook Multi Key TME (MK-TME) aangekondigd, analoog aan AMD’s SEV, maar de nieuwe Xeons hebben Software Guard Extensions (SGX) om versleutelde enclaves in het geheugen op te zetten voor gevoelige data op cloudservers, de zogeheten Trusted Execution Environment. De respectieve sleutels voor geheugenencryptie worden bij AMD bewaard door de Secure Processor (vaak Platform Security Processor (PSP) genoemd), en bij Intel de Converged Security and Management Engine (CSME).

De Epyc kan ook PCIe-lanes wisselen voor het cache-coherent verbinden van de in-house Radeon Instinct MI-rekenversnellers en de geheugentoegang daarmee verenigen. AMD noemt dat Infinity Architecture. Bij Intel wordt dat alleen verondersteld te komen met Sapphire Rapids en PCIe 5.0 als Compute Express Link (CXL). Het valt nog te bezien of dergelijke functies buiten bij supercomputers op grote schaal zullen worden gebruikt.

Een voordeel van de Xeons – dat in theorie fors is, maar in de praktijk zelden bruikbaar – zijn de twee AVX-512 reken-units per core. Die verwerken tweemaal zoveel data per kloktik als de twee AVX-2-eenheden per Epyc-core. Intel heeft de AVX-512-units ook nieuwe AI-trucjes geleerd, namelijk Vector Neural Network Instructions (VNNI) en Deep Learning Boost (DL Boost). Als software met AVX-512-code wordt uitgevoerd, kunnen Ice Lake-Xeons de Epycs met veel meer cores dus achter zich laten. Maar ten eerste is AVX-512-code zeldzaam, ten tweede hebben Epycs meer cores, ten derde zijn ze vaak hoger geklokt dan Xeons en ten vierde worden rekenversnellers vaak gebruikt voor high-performance computing (HPC) en AI-algoritmes. Hoe de toekomst van AVX-512 eruit zal zien is nog onduidelijk omdat Intel zelf binnenkort een uitbreiding zal inbouwen met de naam Advanced Matrix Extensions (AMX), die AVX-units vaak overbodig maakt. Naar verluidt zullen programmeurs dergelijke reken-units makkelijk kunnen gebruiken dankzij Intels OneAPI.

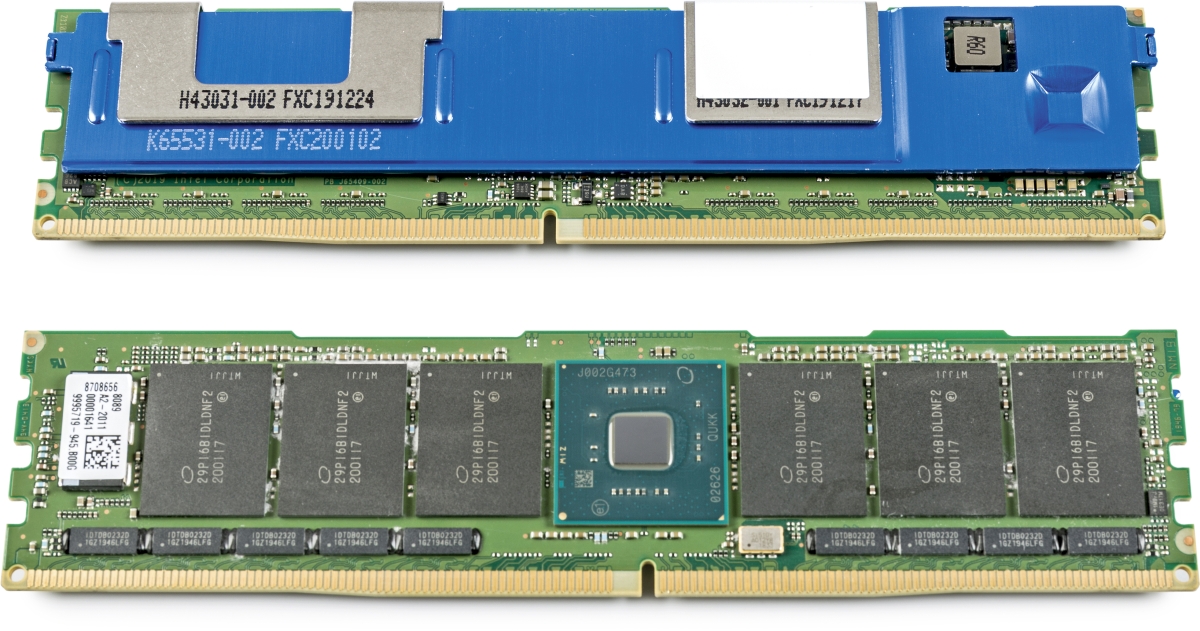

De AVX-512-units van de Ice Lake-Xeons kunnen ook sommige algoritmes voor encryptie en decryptie veel sneller verwerken, zoals AES en ECDHE. Intels non-volatile geheugenmodules met zeer hoge capaciteit (Optane DC Persistent Memory) kunnen alleen worden gebruikt met Xeons. De Ice Lakes hebben de nieuwe versie Pmem 200 alias Barlow Pass nodig (Pmem 100: Apache Pass), die verkrijgbaar is als geheugenmodules met een capaciteit van 128, 256 of 512 GB. Optane is trager dan DRAM, maar goedkoper per gigabyte, en duurder dan NVMe-ssd’s, maar veel sneller. Als combinatie van DDR4- en Pmem 200-modules is in een dual-socket Xeon-server tot 12 TB geheugen mogelijk. Optane-geheugen kan worden gebruikt als goedkope RAM-vervanger en ook voor speciale functies van database- en opslagservers.

Conclusie

De derde Epyc-generatie 7003 heeft slechts kleine, maar goed werkende verbeteringen, maar de Ice Lake-Xeons presteren duidelijk beter dan hun voorgangers. Maar het is too little too late: zelfs de nieuwe Xeon-topmodellen lopen bij veel disciplines achter op de Epycs – en vaak zelfs achter op de oudere Epyc 7742.

Met identieke hoeveelheden cores en geheugen zouden de prestatieverschillen tussen systemen met Milan en Ice Lake echter moeten wegsmelten. Voor servers voor algemeen gebruik, die vaak zijn uitgerust volgens het principe van zoveel mogelijk cores en geheugen voor zo weinig mogelijk geld, zal de prijzenoorlog tussen AMD en Intel waarschijnlijk heviger worden.

Als het gaat om speciale toepassingsgebieden zoals cloudservers voor Confidental Computing, supercomputers of AI-systemen, komen de exclusieve kenmerken van de concurrerende processors in het spel: SEV en Infinity Architecture aan Epyc-zijde, SGX, VNNI en Optane-geheugen op de Xeons. PCI Express 4.0 brengt, onafhankelijk van de rekenkracht van cpu’s, meer snelheid voor ssd’s en rekenversnellers – uiteindelijk ook bij Xeons.

Tip

Krijg direct toegang tot alle beschikbare edities op je laptop, tablet of smartphone.

Praat mee